# Hardware Design Specification

| Project:  | Xbox             |

|-----------|------------------|

| Author:   | leodelc, ggibson |

| Revision: | 0.91             |

| Date:     | 11/2/2000        |

# **Proprietary Notice**

The information contained herein is confidential, is submitted in confidence, and is proprietary information of Microsoft Corporation, and shall only be used in the furtherance of the contract of which this document forms a part, and shall not, without Microsoft Corporation's prior written approval, be reproduced or in any way used in whole or in part in connection with services or equipment offered for sale or furnished to others. The information contained herein may not be disclosed to a third party without consent of Microsoft Corporation, and then, only pursuant to a Microsoft approved non-disclosure agreement. Microsoft assumes no liability for incidental or consequential damages arising from the use of this specification contained herein, and reserves the right to update, revise, or change any information in this document without notice.

Published by

X-box Console Group

Microsoft Corporation One Microsoft Way Redmond, WA 98052-6399 Telephone (425) 882-8080

©1999-2000 Microsoft Corporation. All rights reserved. Printed in the USA.

Microsoft, MS-DOS, and MS are registered trademarks and Windows is a trademark of Microsoft Corporation.

# Contents

| 1. OVERVIEW                                        | 12 |

|----------------------------------------------------|----|

| 1.1. Xbox Game System Architecture                 | 13 |

| 1.2. Xbox Console Architecture                     | 14 |

| 1.3. Software Architecture                         | 15 |

| 1.4. Front Panel Features                          | 15 |

| 1.4.1. Power Switch                                | 15 |

| 1.4.2. Game Controller Ports                       | 16 |

| 1.4.3. Disk Eject                                  | 16 |

| 1.4.4. Indicator Lights                            | 16 |

| 1.5. Rear Panel Features                           | 16 |

| 1.5.1. Power IN                                    | 16 |

| 1.5.2. Audio Video Interface Port (AVIP)           | 16 |

| 1.5.3. Network Interface                           | 16 |

| 1.6. System Durability Requirements                | 17 |

| 1.6.1. Reliability Requirements                    | 17 |

| 1.6.2. Environmental Requirements                  | 18 |

| 1.6.3. Shipping Requirements                       | 19 |

| 2. DESIGN SPECIFICATIONS                           | 20 |

| 2.1. Central Processing Unit                       | 20 |

| 2.2. System Memory                                 | 20 |

| 2.3. Boot ROM                                      | 21 |

| 2.4. Graphics Subsystem                            | 21 |

| 2.4.1. North Bridge and GPU (NV2A)                 | 22 |

| 2.4.2. TV Encoder                                  | 24 |

| 2.5. Audio Subsystem                               | 26 |

| 2.5.1. Audio Processing Unit                       | 27 |

| 2.5.2. Digital Audio Interface Controller          | 28 |

| 2.6. Core Logic (MCPX)                             | 29 |

| 2.6.1. Audio Processor and Digital Audio Interface | 30 |

| 2.6.2.   | ATA Interface                   | 30 |

|----------|---------------------------------|----|

| 2.6.3.   | USB Host Controller             | 30 |

| 2.6.4.   | Ethernet MAC                    | 30 |

| 2.6.5.   | General Purpose IO Pins         | 31 |

| 2.6.6.   | Internal Boot ROM               | 31 |

| 2.6.7.   | External ROM Interface          | 32 |

| 2.6.8.   | LPC Interface                   | 32 |

| 2.6.9.   | LDT Bus                         | 32 |

| 2.6.10.  | Clock Generator                 | 33 |

| 2.6.11.  | Real Time Clock (RTC)           | 33 |

| 2.6.12.  | CPU Support Logic               | 34 |

| 2.7. Sys | stem Management Controller      | 36 |

| 2.7.1.   | Pin Out                         | 37 |

| 2.7.2.   | Power Control                   | 38 |

| 2.7.3.   | Temperature Monitoring          | 39 |

| 2.7.4.   | Fan Control                     | 39 |

| 2.7.5.   | Front Panel IO                  | 40 |

| 2.7.6.   | AV Mode Detect                  | 42 |

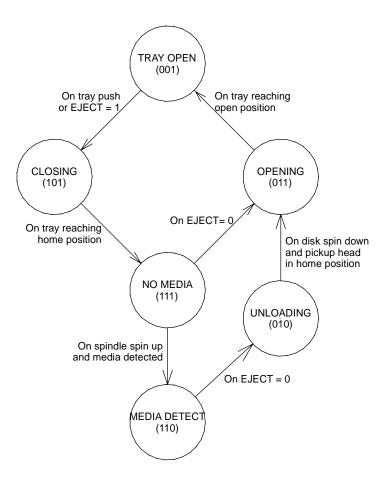

| 2.7.7.   | DVD Tray Control                | 43 |

| 2.8. Sys | stem Clocking                   | 43 |

| 2.8.1.   | System Clocking Architecture    | 43 |

| 2.8.2.   | Clock Generator                 | 44 |

| 2.8.3.   | RTC Clock Specifications        | 47 |

| 2.9. Dig | ital Versatile Disk (DVD) Drive | 47 |

| 2.9.1.   | Media Compatibility             | 47 |

| 2.9.2.   | Format Compatibility            | 48 |

| 2.9.3.   | Spindle Speed Control           | 48 |

| 2.9.4.   | Performance Specifications      | 48 |

| 2.9.5.   | Electrical Specifications       | 51 |

| 2.9.6.   | Functional Requirements         | 54 |

| 2.9.7.   | Software Requirements           | 56 |

| 2.9.8.   | Mechanical Specifications       | 57 |

| 2.9.9.   | Environmental Requirements      | 57 |

| 2.10. H  | lard Disk Drive (HDD)           | 57 |

| 2.10.1.  | General Specifications          | 57 |

|          |                                 |    |

Microsoft ConfidentialFilename: X-Box Hardware Design Specification 0.91.doc

Page 4

| 2.10.2.   | Performance Requirements                                                   | 58     |

|-----------|----------------------------------------------------------------------------|--------|

| 2.10.3.   | Electrical Requirements                                                    | 59     |

| 2.10.4.   | Environment Requirements                                                   | 59     |

| 2.11. No  | etwork Interface                                                           | 59     |

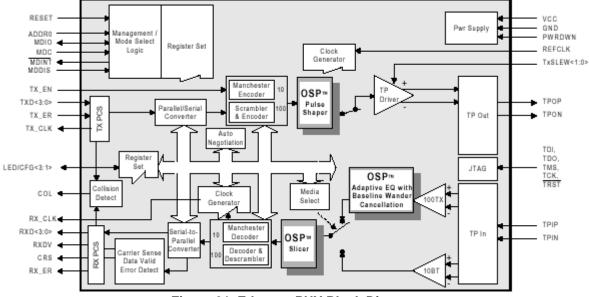

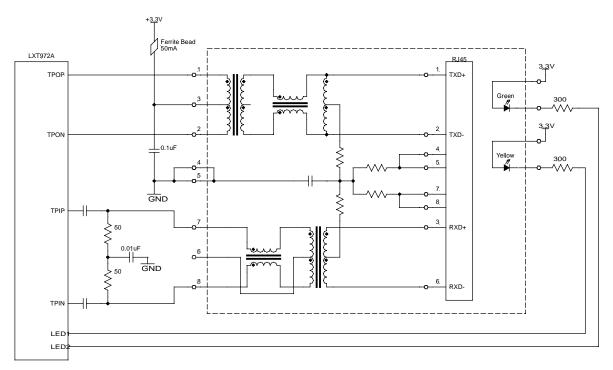

| 2.11.1.   | Ethernet PHY                                                               | 59     |

| 2.11.2.   | Magnetics Specification                                                    | 60     |

| 2.11.3.   | Network Connector                                                          | 61     |

| 2.11.4.   | Interface Circuit                                                          | 61     |

| 2.12. Au  | udio Video Interface Port (AVIP)                                           | 62     |

| 2.12.1.   | Mechanical Connector Characteristics                                       | 62     |

| 2.12.2.   | DC Power Output                                                            | 65     |

| 2.12.3.   | Mode Selection Inputs                                                      | 65     |

| 2.12.4.   | Digital Audio Output                                                       | 65     |

| 2.12.5.   | Analog Audio Output                                                        | 66     |

| 2.12.6.   | Video Outputs                                                              | 68     |

| 2.12.7.   | SCART Status Output                                                        | 73     |

| 2.13. Co  | ontroller Interface Port                                                   | 75     |

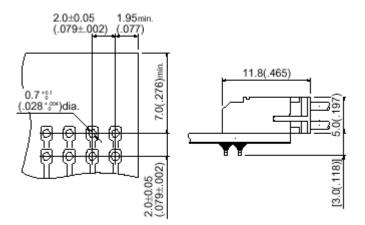

| 2.13.1.   | Mechanical Specification                                                   | 75     |

| 2.13.2.   | DC Power Output                                                            | 76     |

| 2.13.3.   | Digital Communication                                                      | 78     |

| 2.13.4.   | Video Sync Signal                                                          | 78     |

| 2.14. LF  | PC Header                                                                  | 78     |

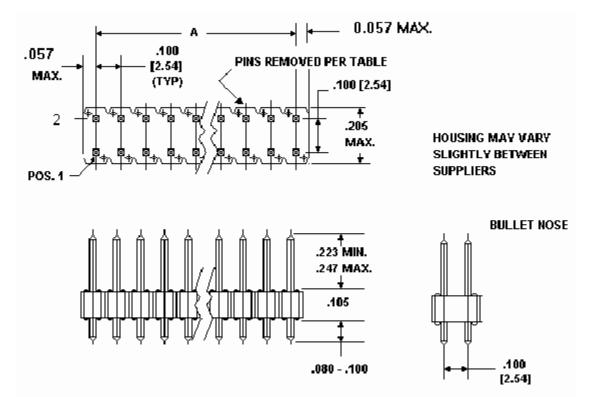

| 2.14.1.   | Mechanical Specification                                                   | 79     |

| 2.14.2.   | Signal List                                                                | 80     |

| 2.15. Po  | ower Supply                                                                | 80     |

| 2.15.1.   | System Power Budget                                                        | 81     |

| 2.15.2.   | System PSU                                                                 | 81     |

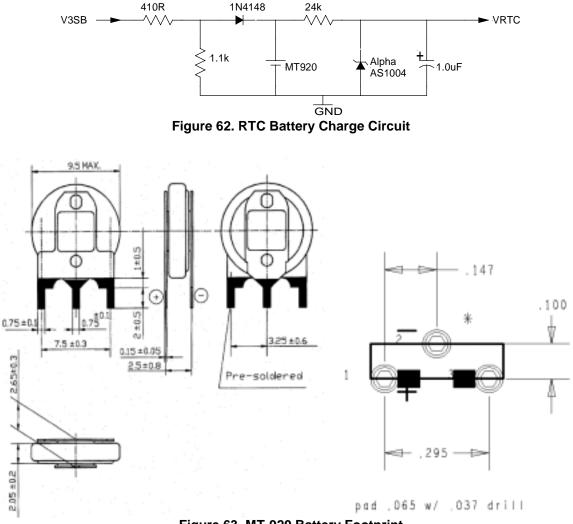

| 2.15.3.   | RTC Power Supply                                                           | 83     |

| 2.15.4.   | Local Voltage Regulators                                                   | 84     |

| 3. ХВОХ   | ACCESSORIES                                                                | 86     |

| 3.1. Gan  | ne Controller                                                              | 86     |

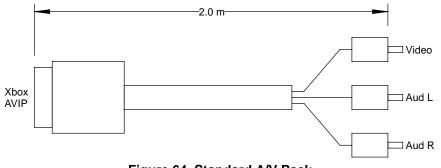

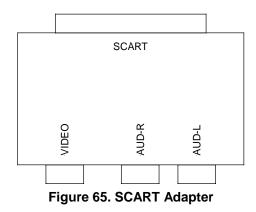

| 3.2. AV I | Packs                                                                      | 86     |

| 4. SYSTE  | EM INTEGRATION                                                             | 93     |

| Mic       | crosoft ConfidentialFilename: X-Box Hardware Design Specification 0.91.doc | Page 5 |

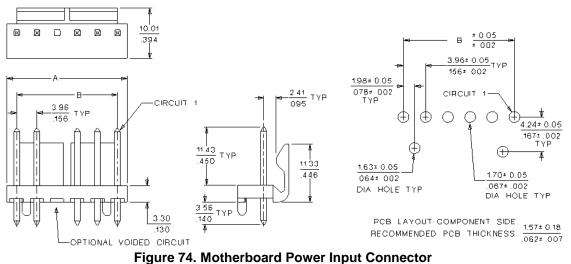

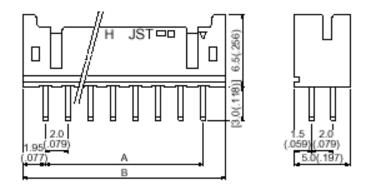

| 4.1.  | Мо   | therboard Printed Circuit Board Assembly                                   | 94     |

|-------|------|----------------------------------------------------------------------------|--------|

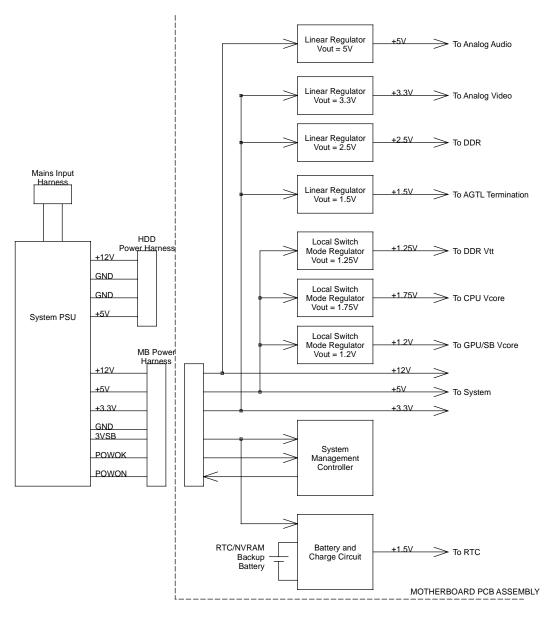

| 4.1   | .1.  | System Power                                                               | 94     |

| 4.1   | .2.  | ATA                                                                        | 95     |

| 4.1   | .3.  | Controller 1/2 Port                                                        | 95     |

| 4.1   | .4.  | Controller 3/4 Port                                                        | 95     |

| 4.1   | .5.  | Front Panel                                                                | 96     |

| 4.1   | .6.  | DVD Power/Control                                                          | 96     |

| 4.1   | .7.  | Fan                                                                        | 97     |

| 4.2.  | Sys  | stem Fan Assembly                                                          | 97     |

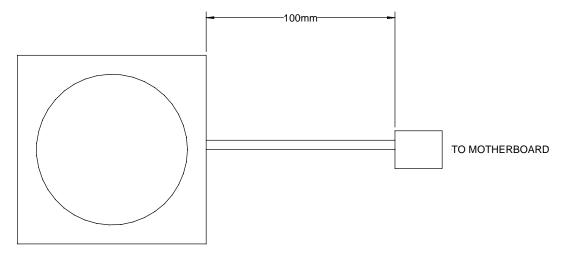

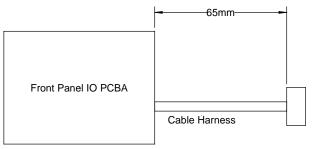

| 4.3.  | Fro  | nt Panel IO Subassembly                                                    | 98     |

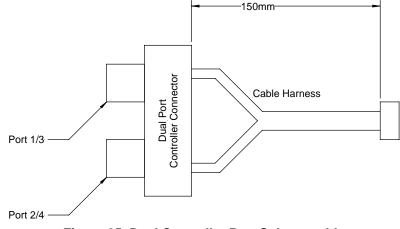

| 4.4.  | Du   | al Controller Port Subassembly                                             | 99     |

| 4.5.  | Sys  | stem PSU                                                                   | 99     |

| 4.5   | 5.1. | System Power                                                               | 99     |

| 4.5   | 5.2. | HDD Power Harness                                                          | 100    |

| 4.6.  | DV   | D Drive                                                                    | 101    |

| 4.6   | 5.1. | ATA Connector                                                              | 101    |

| 4.6   | 6.2. | Power/Control Connector                                                    | 101    |

| 4.7.  | DV   | D Power/Control Cable Assembly                                             | 101    |

| 4.8.  | Hai  | d Disk Drive                                                               | 102    |

| 4.8   | 3.1. | ATA Connector                                                              | 102    |

| 4.8   | 8.2. | Power Connector                                                            | 102    |

| 4.9.  | AT.  | A Cable Assembly                                                           | 102    |

| APPEN | IDIX | A – POWER BUDGET SPREADSHEET                                               | 103    |

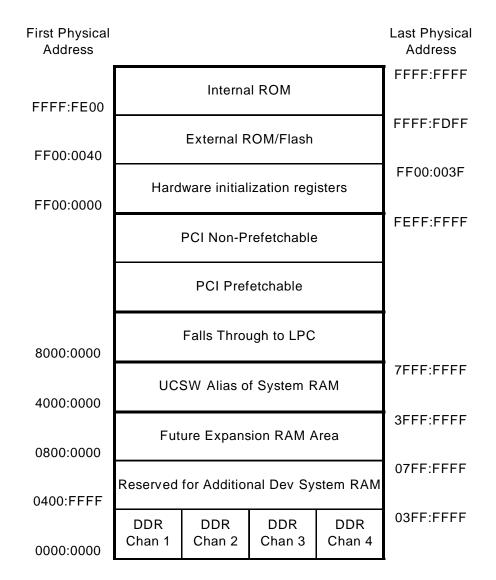

| APPEN | IDIX | B – SYSTEM MEMORY MAP                                                      | 105    |

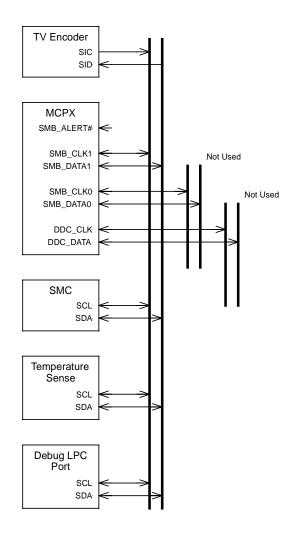

| APPEN | IDIX | C – SM BUS ADDRESS MAP                                                     | 106    |

| APPEN | IDIX | D – TELEVISION SYSTEMS USED BY COUNTRY                                     | 107    |

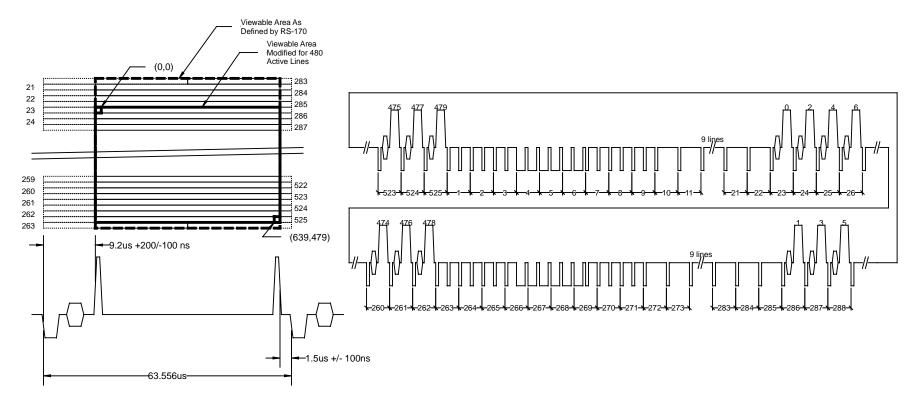

| APPEN | IDIX | E – VIDEO WAVEFORM TIMING                                                  | 108    |

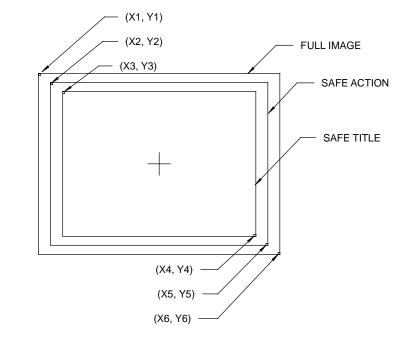

| APPEN | IDIX | F – SAFE ACTION AND SAFE TITLE GUIDELINES                                  | 109    |

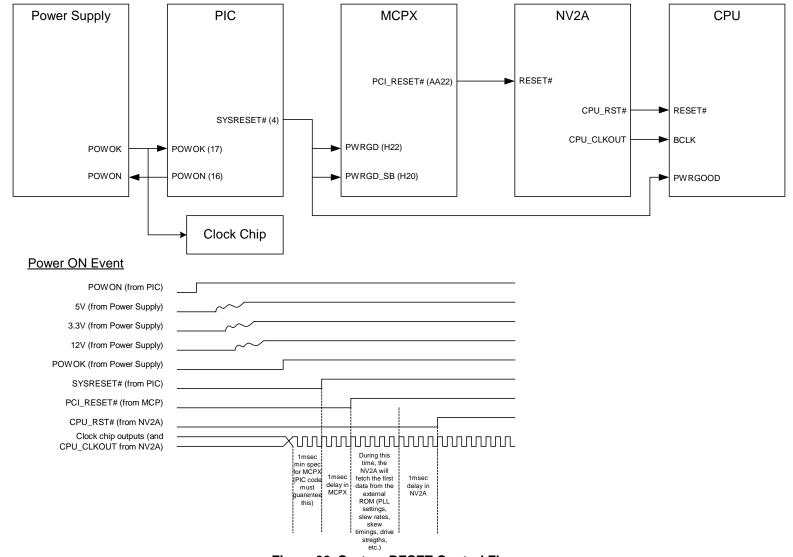

| APPEN | IDIX | G – SYSTEM RESET FLOW CONTROL                                              | 110    |

|       | М    | crosoft ConfidentialFilename: X-Box Hardware Design Specification 0.91.doc | Page 6 |

# **Revision History**

| Revision | Date       | Description                                                                                                      | Author/Revised by |

|----------|------------|------------------------------------------------------------------------------------------------------------------|-------------------|

| 0.1      | 10/11/1999 | Initial draft based on preliminary<br>work of exploratory team,<br>presentations, and meeting notes              | leodelc           |

| 0.2      | 10/14/99   | Added detail                                                                                                     | leodelc, ggibson  |

| 0.3      | 10/25/99   | Reviewed at potential supplier                                                                                   | leodelc, ggibson  |

| 0.4      | 10/26/99   | Updated during manufacturing review                                                                              | leodelc           |

| 0.5      | 10/28/99   | Minor updates                                                                                                    | ggibson           |

| 0.51     | 10/29/99   | Removed references to 3 <sup>rd</sup> party<br>component names & features                                        | ggibson           |

| 0.61     | 11/12/99   | Revise front and rear panel<br>connection requirements, a/v<br>connector requirements, and<br>audio requirements | leodelc           |

| 0.62     | 11/22/99   | Added 1394 & USB to rear panel; updated power supply section                                                     | ggibson           |

| 0.63     | 11/24/99   | Updated AV Pack descriptions                                                                                     | leodelc           |

| 0.64     | 12/10/99   | Added HDD detailed specification.<br>Added system reliability,<br>environmental and shipping<br>specifications   | leodelc           |

| 0.65     | 1/12/00    | Updated block diagram to reflect<br>recent major product definition<br>decisions.                                | leodelc           |

|          |            | Eliminate 1394, Modem.                                                                                           |                   |

|          |            | Integrate NB logic into GPU                                                                                      |                   |

|          |            | UMA                                                                                                              |                   |

|          |            | Eliminate HDTV requirements                                                                                      |                   |

|          |            | Added SMBus requirement to<br>core logic.                                                                        |                   |

| 0.66     | 2/16/00    | Incorporate details from<br>motherboard kickoff meeting.                                                         | leodelc           |

|          |            | Completed preliminary detailed<br>power budget and PSU<br>specification.                                         |                   |

| 0.67     | 2/25/00    | Added Modem requirements and<br>improved HDD and DVD drive<br>requirements section                               | leodelc           |

| 0.68     | 3/2/00     | Updated per MRD                                                                                                  | leodelc           |

|          |            | AV Pack specs complete                                                                                           |                   |

| 0.69     | 3/15/00    | Added Video output requirements                                                                                  | leodelc           |

|          |            | Updated DVD drive spec detail                                                                                    |                   |

|          |            | Eliminated RESET switch                                                                                          |                   |

| Revision | Date     | Description                                                                                           | Author/Revised by |

|----------|----------|-------------------------------------------------------------------------------------------------------|-------------------|

| 0.7      | 4/14/00  | Added core logic descriptions and added detail for DVD, modem, TV encoder, and audio codec            | leodelc           |

| 0.71     | 5/1/00   | Added detail                                                                                          | leodelc           |

| 0.72     | 5/10/00  | Updated DVD specification based<br>on vendor feedback                                                 | leodelc           |

| 0.73     | 5/18/00  | Updated based on MCPX review and additional feedback                                                  | leodelc           |

|          |          | Introduced a new section for<br>system integration and definitions<br>for major system sub assemblies |                   |

|          |          | Updated AV Pack configurations                                                                        |                   |

| 0.74     | 5/30/00  | Updated system PSU spec                                                                               | leodelc           |

|          |          | Eliminated VESA AV Pack                                                                               |                   |

|          |          | Added system clocking<br>architecture                                                                 |                   |

| 0.75     | 7/5/00   | Eliminated redundant<br>specifications covered in detailed<br>documents (PSU, DVD)                    | leodelc           |

|          |          | Updated system assembly details                                                                       |                   |

|          |          | Updated AVIP pinout to optimize motherboard layout                                                    |                   |

|          |          | Updated video filter requirements                                                                     |                   |

| 0.9      | 7/28/00  | Updated Modem spec                                                                                    | leodelc           |

|          |          | Updated AV Pack specs                                                                                 |                   |

|          |          | Updated ATA cable lengths                                                                             |                   |

|          |          | PIT clock defined @25MHz                                                                              |                   |

|          |          | Added APICLK requirement                                                                              |                   |

|          |          | Incorporated feedback from Intel review                                                               |                   |

|          |          | Removed rear expansion port                                                                           |                   |

|          |          | HW initialization region in boot<br>ROM increased to 256 bytes                                        |                   |

|          |          | Added system RESET, SMBus,<br>Interrupt mapping                                                       |                   |

|          |          | Swapped DVDEJECT and SMI on SMC pinout.                                                               |                   |

| 0.91     | 10/19/00 | Updated based on input from team review                                                               | leodelc           |

# **Reference Documents**

This document references the following documents:

#### **Microsoft Specifications Documents**

System Management Controller Firmware Specification, Revision 0.2, 9/26/2000

DVD-ROM Drive Specification, Revision 0.85, 6/19/2000

Power Supply Design Specification, Revision 0.92, 8/3/2000

Xbox 3<sup>rd</sup> Party Game Controller Specification, Doc No. QQ101Revision 0.92, August 23, 2000

#### **Component Data Sheets**

Desktop Pentium(R) III Processor in BGA2 Package Electrical, Mechanical, and Thermal Specification. Intel Reference Number FM-1923

NV2A (Xbox Graphics Processing Unit) Design Specification, Revision 0.5, September 11, 2000

*Flicker-Free Video Encoder with Ultrascale Technology*, Conexant Document Number 100381A, February 2000

MCP-1 Media Communication Processor (South Bridge), Version 0.15, August 2000

*LXT972A 3.3V Dual-Speed Fast Ethernet Transceiver*, Revision 1.1, Level One Document Number IS972DS-R1.1-0200, February 2000

AC-Link Interface Audio DAC, WM9709 Advance Information, Rev 1.0, June 2000

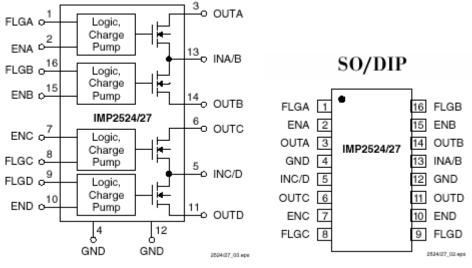

Quad USB High-Side Power Switch With Fault Detection, IMP2524/7, IMP Publication #5005 Rev A, 5/17/00

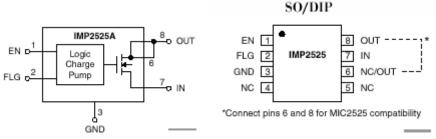

Low Resistance USB High-Side Power Switch, IMP Publication #5001 Rev A, 10/27/99

Lithium Batteries Handbook, Panasonic, August 1998

8-Bit CMOS Microcontrollers with A/D Converter, PIC16C63A/65B/73B/74B, Microchip DS30605B

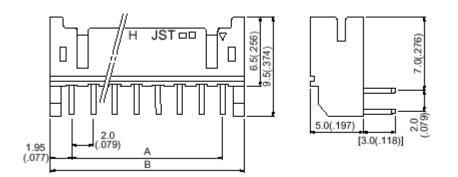

Molex Connector,

*U Series 5 Family Product Manual*, Seagate Publication Number: 20400172-001, Rev. B, August 2000

Western Digital EIDE Hard Drive, WD Protégé Technical Reference Manual, Western Digital Document Number 2679-001008-000, 9/7/00

Dual PUSB Cable Harness, Foxlink P/N PU23310-C, Rev 0.1

Mechanical Package Specification Candyland Control PCB,

Fiber Optic Transmitter Module, TOTX178A, Toshiba, 2000-02-18

#### **Industry Standards Documents**

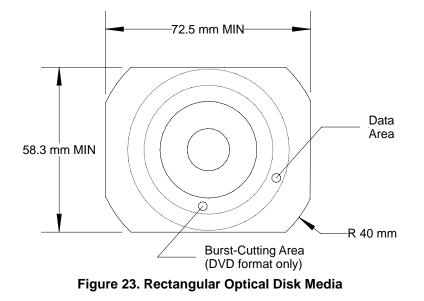

Standard Definition TV Analog Component Interface, EIA-770.2-A, December 1999 High Definition TV Analog Component Video Interface, EIA-770.3, September 1998 120mm DVD Read-Only Disk, Standard ECMA-267, 2<sup>nd</sup> Edition, December 1999 80mm DVD Read-Only Disk, Standard ECMA-268, 2<sup>nd</sup> Edition, December 1999. AT Attachment with Packet Interface Extension - (ATA/ATAPI-4), ANSI NCITS 317-1998 Suite of 3.5" Form Factor Specifications, ANSI SFF-8300, Rev 1.1, June 5, 1995

Specification for ATA 40-pin Connector, ANSI SFF-8059, Rev 2.5, July 31, 1998

Digital audio interface – Part 1 General, IEC 60958-1,

Digital audio interface - Part 3 Consumer Applications, IEC 60958-3,

Audio, video and audiovisual systems - Interconnections and matching values - Preferred matching values of analogue signals, IEC-61938,

Universal Serial Bus Specification, Version 1.1

IEC-60320, Power inlet defintion

IEEE 802.3, Ethernet spec

Low Pin Count (LPC) Interface Specification, Revision 1.0, September 29, 1997

Installable LPC Debug Module Design Guide, Revision 1.0, Intel,

IEC-60320

IEEE 802.3u

ANSI SFF 8059

This reference list in incomplete

# Approvals

| Approved by: |                                               | Date: |

|--------------|-----------------------------------------------|-------|

|              | Todd Holmdahl, HW Development Manager         |       |

| Approved by: |                                               | Date: |

|              | Leonardo Del Castillo, Electrical Engineering |       |

| Approved by: |                                               | Date: |

|              | Greg Gibson, Electrical Engineering           |       |

| Approved by: |                                               | Date: |

|              | Rob Walker, Electrical Engineering            |       |

| Approved by: |                                               | Date: |

|              | Woody Beverly, Firmware Engineering           |       |

| Approved by: |                                               | Date: |

|              | Jeff Reents, Mechanical Engineering           |       |

| Approved by: |                                               | Date: |

|              | Dick Liu, Mechanical Engineering              |       |

| Approved by: |                                               | Date: |

|              | Jon Wilcox, HW Test Lead                      |       |

| Approved by: |                                               | Date: |

|              | Jim Stewart, Industrial Design                |       |

| Approved by: |                                               | Date: |

|              | Tom Brooks, Usability                         |       |

| Approved by: |                                               | Date: |

|              | Jon Thomason, Software Development Manager    |       |

| Approved by: |                                               | Date: |

|              |                                               |       |

| Approved by: |                                               | Date: |

|              |                                               |       |

| Approved by: |                                               | Date: |

|              |                                               |       |

# 1. Overview

The Xbox is a variation of the legacy-free PC architecture designed to target the game console and living room entertainment space. The Xbox product definition targets four key aspects, including minimal retail price, excellent graphics and sound performance, enhanced television viewing, and Internet capability.

This document specifies the hardware design of the Xbox gaming console, including specification of the following system-critical design aspects:

Central Processing Unit (CPU)

Main memory cache capacity and performance

Main memory capacity and bandwidth

3-D Accelerated Graphics Processor architecture, performance and memory capacity

3-D Accelerated Audio Processor

Audio and Video Outputs

Universal Serial Bus implementation

Digital Versatile Disk specification

**Boot-ROM** implementation

Hard Disk Drive specification

Core logic implementation

The architecture of the Xbox is based on leading edge PC technology. The architecture and performance of the Xbox shall remain constant through the life span of the product, which is estimated at approximately 4 years. Over this span of time, PC technology will continue to advance, while average PC prices fall at a fairly low rate. The Xbox, however, shall maintain consistent performance year over year, while decreasing the cost of manufacture and the retail price of the product.

The long-term requirements of the design are:

Fast time to market of initial design

Rock-solid reliability

Best-in-class performance compared to current PC designs

Significantly better performance relative to contemporary game consoles

Path to achieve cost reduction of 30% annually

Uniform performance over time, independent of implementation

# 1.1. Xbox Game System Architecture

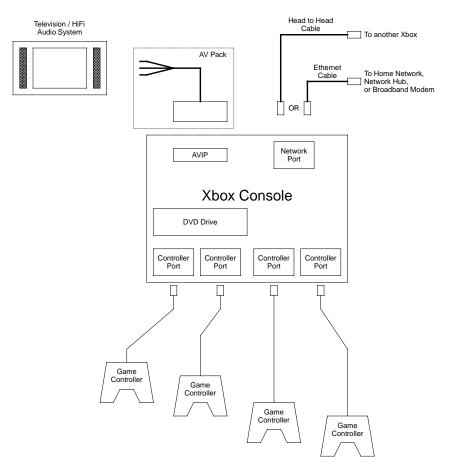

The Xbox game system consists of the Xbox console, one or more game controllers, an AV Pack, a television monitor, and an audio reproduction system. Refer to the diagram below for the following description of the game system, the components involved, and their interconnection.

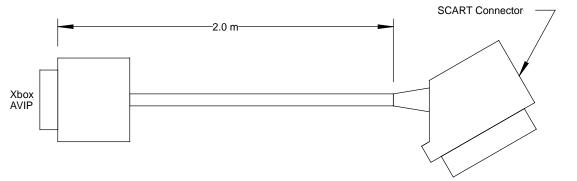

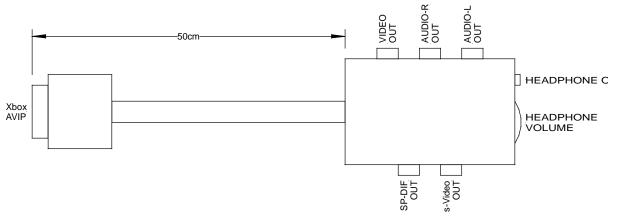

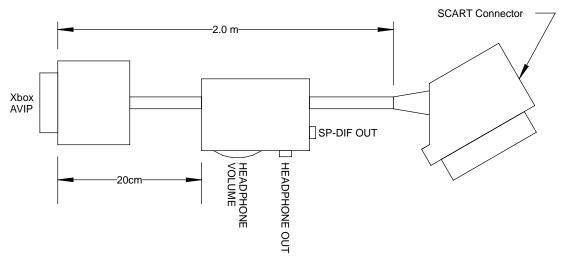

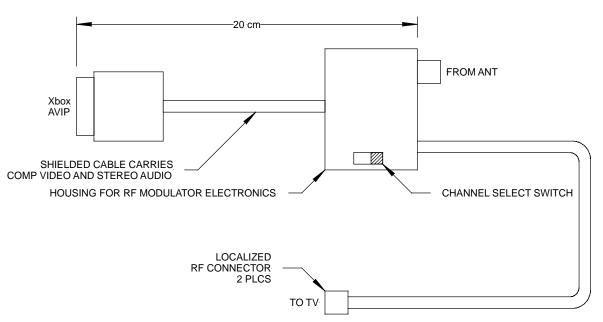

Figure 1. Xbox Game System

The Xbox game console has three interface ports; controller interface ports, the Audio Video Interface Port (AVIP), and the network port. The controller ports, located on the front of the console provide a means of connecting game controllers to the console. Game controllers are the primary user input devices for the console. The AVIP is a multi-pin connector that carries all the signals required to connect the Xbox console to a television and audio system. The Xbox supports many type of interconnection methods. An AV Pack is an accessory device that adapts the AVIP to the particular needs of the user's audio visual system. There are AV Packs that provide composite video and line level audio signals, RF modulated signal, and high-quality component video signals.

The network interface port provides a means of networking several Xbox consoles together for head to head or group game play. Networking may be peer-to-peer, local area network, or broadband via the Internet.

# **1.2. Xbox Console Architecture**

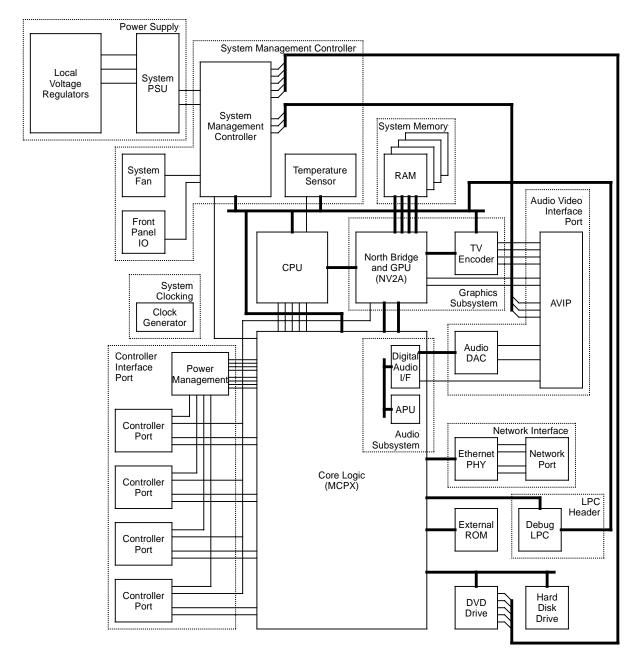

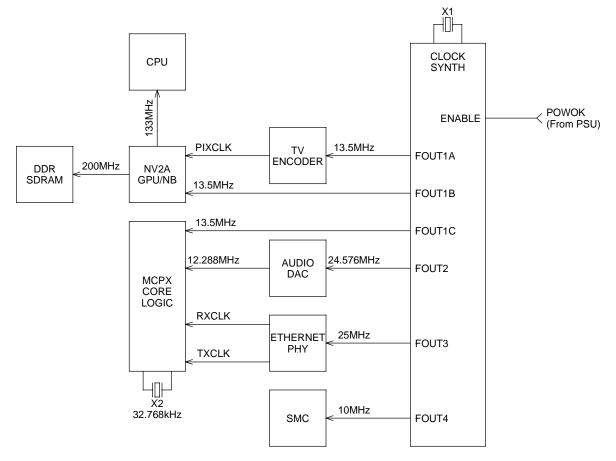

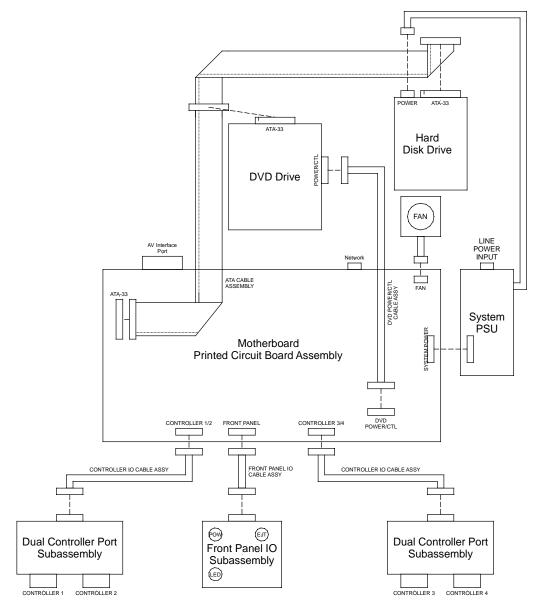

The figure below shows the system-level block diagram of the Xbox console.

Figure 2. Xbox System Block Diagram

The remainder of this section describes the features of the Xbox design. Subsequent sections shall describe the detailed design and implementation guidelines and performance specifications required to implement the described feature set.

# 1.3. Software Architecture

This document does not presume to cover the detailed software architecture of the Xbox, but the following sections provide a high-level overview of the architecture of the OS, and how it is related to the hardware design of Xbox for the first and following years.

The Xbox Operation System is divided into two pieces, the XROM and the Xbox Title Library (XTL). The XROM is the kernel of the XOS operating system. It provides the hardware initialization code, XOS kernel, decryption and code signature verification, application loading, and the drivers for some of the hardware features. The XTL is provided to the application developer as a linkable library, becoming part of the executable code loaded from the DVD media. The XROM is specific to a particular console design, whereas the XTL is generic and must be able to work with any iteration of the Xbox hardware design.

An Xbox application primarily controls and configures the Xbox hardware by calling the XOS API, however, an application may also access some parts of the Xbox hardware directly, in an effort to provide the most efficient performance. For the performance-critical features of the Xbox, the hardware implementation will remain exactly the same, and so direct access to these hardware features will be the same throughout the product life of the Xbox. In general, any hardware feature normally handled by the XTL may also be accessed directly by the application.

Some aspects of the Xbox hardware design, however, have no impact on application performance, and may undergo changes from year to year as the Xbox design is cost optimized. The code to configure, control, and communicate with these features is implemented in the XROM. An application must never directly access these hardware features.

The components that must never be accessed directly by the application are listed below:

- System Management Controller

- Ethernet PHY Transceiver

- TV Encoder

- DVD drive

- Hard Disk Drive

- Second USB Host Controller

- Real Time Clock

- GPIO pins of the MCPX

- Ethernet MAC

# **1.4.** Front Panel Features

This section briefly describes the features of the Xbox console at the system level. A detailed description of the functionality, implementation, and specifications for each feature can be found in the later sections of this document.

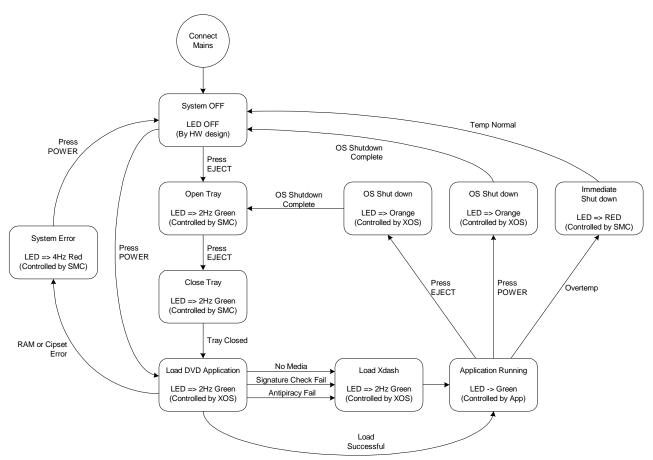

### 1.4.1. Power Switch

The power switch is a momentary type push switch, monitored by the System Management Controller (SMC), which in turn monitors the system power up and power down cycle. The design implements soft power up and power down, allowing the system to perform cleanup operations prior to shutdown. At the same time, the SMC guarantees the system will shut down reliably in the case of a system crash. The Xbox does not implement any meta-power states. The console itself is either "on" or "off", although the SMC is always on as long as mains power is applied.

### 1.4.2. Game Controller Ports

Four front-mounted game controller ports are required. Electrically, each port appears as a fullspeed upstream USB port, but mechanically, the connector is proprietary. The proprietary connector is designed to meet the Xbox product requirements for pull force and cycle life.

## 1.4.3. Disk Eject

The disk eject button is also monitored by the SMC. This allows the disk eject function to be operated even if the power is "off", so long as mains power is applied.

## 1.4.4. Indicator Lights

The EJECT switch is surrounded by a light pipe illuminated by a pair of red and green LEDs. The LEDs are controlled by the SMC based on the SMC state machine and software settings requested by the CPU. The behavior of these LEDs is described in detail in the SMC section.

# **1.5. Rear Panel Features**

### 1.5.1. Power IN

The power input shall be AC line power, via a removable 2-pin line cord conforming to IEC-60320 2.5A Plug Connector for Class II Equipment. The input voltage range shall be constrained to "low range" (approximately 110V) or "high range" (approximately 240V) depending on the regional market in which the console is sold.

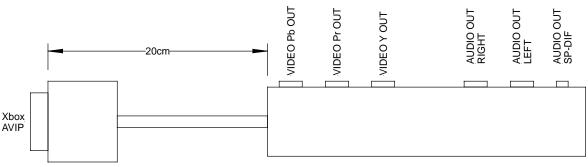

# 1.5.2. Audio Video Interface Port (AVIP)

This multi-pin port consists of all electrical input and output ports supported by the graphics processor and audio codec. The AVIP includes video output signals, audio output signals, and selector inputs used to identify the type of adapter connected to the AVIP port.

By setting the logic states of the AVIP inputs, the adapter may select CVBS+Y/C (NTSC, PAL, or SECAM), CVBS + RGB (PAL SCART) or YPrPb HDTV outputs. The AVIP has two audio interface ports; line-level stereo audio (left and right channels) is output directly, and a logic-level SPDIF output is provided for interface to an external coaxial or fiber optic driver.

## 1.5.3. Network Interface

The network interface is implemented as a 10/100-Base T (RJ-45) Ethernet port. This port provides access to broadband Internet connections such as cable modems, DSL modems, home networks, and peer-to-peer networking. The PHY layer and MAC shall support 10 and 100 Mbit/s operation (IEEE 802.3u).

# **1.6.** System Durability Requirements

This section describes the system environmental and reliability requirements. This section is provided only for reference, the actual requirements of the electrical design will be affected by the mechanical enclosure and thermal management system.

|                                      | Spec Requirement                 | Comments                                                                                                                        |

|--------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mean Product Life                    | 9000 hrs @ 25C                   | Product warranty will be 90 days                                                                                                |

|                                      | 2000 hrs @ 45C                   | Mean life represents operational hours at indicated ambient temperatures                                                        |

| Total DPM                            | 10,000                           | Total yield, including infant mortality                                                                                         |

| Factory DPM                          | 5000                             |                                                                                                                                 |

| 30-day Infant Mortality DPM          | 5000                             |                                                                                                                                 |

| Mean Time To Failure                 | 250k hours @ 25C                 | This figure represents the steady-state failure rate of units in the field, excluding infant failures and end of life failures. |

|                                      |                                  | The failure rate for 5M units used 4hrs/day $\approx$ 30k units/year                                                            |

| Service Life                         | 8000 hrs @ 25C<br>2000 hrs @ 45C | This corresponds to 4-5 hours per day for 5 years.                                                                              |

| Connector reliability                | 2000 cycles                      | All user-accessible connectors                                                                                                  |

| DVD loader reliability               | 10,000 load/unload<br>cycles     | This may need to be increased based on typical usage scenario.                                                                  |

| DVD Eject Button                     | 20,000 cycles                    | This may be reduced as this level of reliability may exceed the typical usage scenario.                                         |

| Power cycling and switch reliability | 20,000 cycles                    | This may be reduced as this level of reliability may exceed the typical usage scenario.                                         |

| Power switch bounce                  | 10ms max.                        |                                                                                                                                 |

# 1.6.1. Reliability Requirements

|                                               | Spec Requirement                                                                                                    | Comments                                                                                                                                                                                                                                                                                |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Temperature                         | 5 to 45C                                                                                                            | External ambient air temperature.<br>Assume box is placed on a hard surface<br>that is at thermal equilibrium with the<br>ambient air.                                                                                                                                                  |

| Operating Humidity                            | 5 to 85%RH                                                                                                          | Non-condensing                                                                                                                                                                                                                                                                          |

| Operating Altitude                            | 0 to +2,000 m                                                                                                       | Relative to Mean Sea Level                                                                                                                                                                                                                                                              |

| Maximum operating tilt                        | 10°                                                                                                                 | The unit may be tilted from the horizontal plane up to this angle in any direction.                                                                                                                                                                                                     |

| Maximum power dissipation                     | 200W                                                                                                                | Input power to the unit.                                                                                                                                                                                                                                                                |

| Harmonic Current<br>Emissions                 | Per IEC-61000-3-2<br>as required by locale                                                                          | European and Japanese versions of the product are subject to this standard.                                                                                                                                                                                                             |

| Max external case temperature                 | 50C (buttons)<br>60C (case)                                                                                         | Measured at any point on the external surface, at an external ambient temperature of 25°C. Installed per IEC-60065.                                                                                                                                                                     |

| System Acoustic Noise<br>(Nominal conditions) | < 32dB<br>measured @ 1m<br>(< 28dB Goal)                                                                            | Measured in anechoic chamber with<br>background noise level at least 10dBA<br>below the expected measured level.<br>This measurement made at standard<br>operating conditions of $T_A=25C$ , with the<br>DVD drive reading sequential tracks on<br>the disk, and the HDD spinning idle. |

|                                               | -40 to 60°C, 40C/min ramp, 100 cycles                                                                               | No functional failures allowed.                                                                                                                                                                                                                                                         |

| Thermal Shock                                 | with power applied                                                                                                  | The thermal gradient is maintained without condensation.                                                                                                                                                                                                                                |

| Unit Drop                                     | 3 random drops from 75 cm on to 6mm<br>carpet over ¾" plywood @ 20-25C                                              | Failure is considered functional damage<br>that is not obviously repairable by the<br>end user. There are no cosmetic<br>requirements after drop testing.                                                                                                                               |

| Chemical Resistance                           | Resistant to short-term exposure to common household cleaning agents, including isopropyl alcohol, coffee and cola. | Acceptance is determined by functional<br>performance only (no cosmetic<br>requirements). Chemicals shall be<br>applied only to outside surfaces for a<br>period of less than one minute.                                                                                               |

|                                               | Resistance to anything commonly found on the human hand, or used to clean consumer electronics                      | This specification applies to the external cosmetic surfaces, and does not imply intrusion of chemicals into the interior of the chassis.                                                                                                                                               |

| UV Stability                                  | Per ASTM D4674-89                                                                                                   | No material degradation allowed. Color<br>changes are acceptable (no<br>requirement). It is desired to restrict<br>color changes to a delta-E less than<br>1.0.                                                                                                                         |

# 1.6.2. Environmental Requirements

A "Functional Failure" is considered to be any permanent component failure that results in the unit becoming unserviceable by the end user. Transient failures during operation, i.e. unit locks up, crashes, or resets, is not considered a functional failure if the user can clear the condition by cycling the power ON switch.

|                                                              | Spec Requirement                                     | Comments                                                                 |

|--------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------|

| Package Drop                                                 | 10 drops, 92cm onto<br>asphalt tile over<br>concrete | No functional or cosmetic failures allowed.                              |

| Package Shock (non-operational)                              | 60 minutes per ASTM<br>D999                          | No functional or cosmetic failures allowed.                              |

| Package Vibration                                            | Random, see H00232                                   | No functional or cosmetic failures allowed.                              |

| Storage Temperature                                          | -40 to 60°C                                          | No functional or cosmetic failures allowed.                              |

| Storage Humidity<br>Up to 50°C Ambient<br>Above 50°C Ambient | 5 to 90%RH<br>5 to 70%RH                             | Non-condensing in all cases. No functional or cosmetic failures allowed. |

| Storage Altitude                                             | -300 to +12,000m                                     | Relative to Mean Sea Level                                               |

# **1.6.3.** Shipping Requirements

# **2.Design Specifications**

# 2.1. Central Processing Unit

The Xbox CPU is an Intel PIII variant based on the Coppermine CPU. The CPU features:

MMX and SSE instruction set enhancements

733MHz internal clock rate

133MHz Front-Side Bus

32k L1 Cache

128k Full-speed L2 Cache integrated on-die

BGA-2 package

Manufactured in a  $0.18\mu$  process in the first year of production, with possible die shrink in following years.

JTAG

For a detailed data sheet, refer to the *Desktop Pentium(R) III Processor in BGA2 Package Electrical, Mechanical, and Thermal Specification* published by Intel. The top-level power requirements are listed below:

| Parameter                                                                 | Min   | Typical | Max          | Unit   |

|---------------------------------------------------------------------------|-------|---------|--------------|--------|

| Core Power Supply<br>VCC <sub>CORE</sub><br>ICC <sub>CORE</sub>           |       | 1.75    | 14.6         | V<br>A |

| AGTL Bus Termination Voltage Supply<br>V <sub>TT</sub><br>I <sub>TT</sub> | 1.365 | 1.50    | 1.635<br>2.7 | V<br>A |

| Total Power Consumption                                                   |       |         | 26           | W      |

#### Figure 3. CPU Electrical Characteristics

# 2.2. System Memory

Xbox uses a unified memory architecture (UMA) to consolidate the system RAM and graphics RAM in to a single memory pool. An advanced memory controller and bus arbitration unit bridges the CPU system bus and the GPU system bus and provides high-speed access to the unified memory pool.

The system will use DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory) memory. DDR SDRAM transfers data words at a sustained 400MHz, using both edges of the 200MHz memory clock.

The size of the unified memory pool is 64MB. The memory space is divided into four fully independent memory channels, each 32-bits wide and capable of four open pages of memory.

The RAM IC's will be soldered directly on to the motherboard to eliminate the need for sockets and DIMM modules. The board layout will incorporate eight 2Mx32 ICs, two on each of the four data channels. The two IC's on each bus will be located opposite each other on top and bottom side of the board, with connections made between closest pins. Since address and data pins will be crossed in this configuration, the memory controller will compensate by multiplexing the pin assignments depending on whether it is accessing the top-side or bottom-side IC. Future redesigns

of the Xbox motherboard may migrate to 4Meg x 32 ICs, but the total number of open pages will remain the same.

| Parameter          | Specification                          |  |

|--------------------|----------------------------------------|--|

| Data transfer rate | 1.6GB/s per channel, 6.4 GB/s combined |  |

| Bus Speed          | 200 MHz DDR                            |  |

| Bus Width (Data)   | 4x32 bits (128 bits total)             |  |

| Voltage            | approximately 2.5V                     |  |

| Parity             | None                                   |  |

The DDR memory bus has the following characteristics:

Note: Detail of the system memory components and specification is pending component qualification and vendor selection.

# 2.3. Boot ROM

The Xbox does not have a traditional BIOS such as found in a traditional PC. Instead, the Xbox boots directly from a Flash-RAM or ROM containing hardware initialization code and the Xbox Operating System (XOS). Early production units will implement the Boot ROM as Flash Memory, but will later migrate to a ROM-based component to minimize cost. The Boot ROM shall not be field-upgradeable or modifiable by the user without disassembly and electrical access to the motherboard.

The XOS shall occupy no more than 1M bytes of ROM. The Boot ROM is interfaced through the core logic. The upper 512 bytes of the 1M space is mapped to ROM internal to the MCPX. The lower 256 bytes of the Boot ROM are reserved for hardware initialization values for the MCPX and NV2A core logic chips. These locations will be read directly by the core logic chips prior to CPU reset.

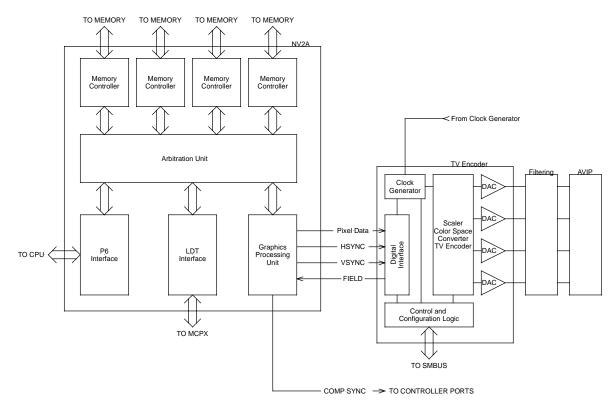

# 2.4. Graphics Subsystem

The graphics subsystem consists of a high-performance memory controller integrated with an advanced graphics processor and a digital video interface to the television encoder. The television encoder includes digital scaling and encoder logic as well as the digital to analog converters for producing NTSC/PAL/SECAM television signals and component YPrPb HDTV signals.

The north bridge functionality is integrated with the graphics processor to implement a Unified Memory Architecture (UMA). The North Bridge consists of a memory controller, a P6 front-side bus interface, an LDT interface, and an arbitration unit to route transactions across the CPU, GPU, LDT, and memory busses. The bus connecting the arbitration unit and the GPU memory bus is internal to the IC. The LDT interface is used to bridge to the companion core logic chip containing the lower-bandwidth logic functions such as ATA, USB, XROM, and the APU. These functions are described in more detail in a subsequent section.

The performance level of the graphics processor is representative of DirectX 8 class PC products. The overall system performance is not only a function of the graphics processor, but also of the busses that interconnect the graphics subsystem and the CPU. The detailed performance criterion for the graphics subsystem components is described in the following sections.

Figure 4. Graphics Subsystem Block Diagram

# 2.4.1. North Bridge and GPU (NV2A)

The NV2A is an integrated North Bridge memory controller and Graphics Processor Unit. The NV2A contains four independent memory controllers for the unified system memory, a P6 front-side bus interface to the CPU, an LDT bus interface to the core logic, a GPU, and an arbitration unit to manage memory and inter-bus transactions.

Refer to the *NV2A Design Specification* for detailed electrical, thermal, and mechanical characteristics. The table below summarizes the system-level characteristics of the NV2A.

| Parameter                                                                        | Min   | Typical | Max                 | Unit        |

|----------------------------------------------------------------------------------|-------|---------|---------------------|-------------|

| Core and LDT Power Supply<br>V1P5<br>I <sub>V1P5</sub><br>Power Consumption      | 1.45  | 1.50    | 1.55<br>7<br>8.4    | V<br>A<br>W |

| LVTTL Interface Supply<br>V3P3<br>I <sub>V3P3</sub><br>Power Consumption         | 3.0   | 3.3     | 3.6<br>TBD<br>TBD   | V<br>A<br>W |

| CPU AGTL+ Termination Supply<br>VAGTL<br>I <sub>VAGTL</sub><br>Power Consumption | 1.385 | 5 1.5   | 1.615<br>TBD<br>TBD | V<br>A<br>W |

| Memory Interface Power Supply<br>V2P5<br>I <sub>V2P5</sub><br>Power Consumption  | 2.3   | 2.5     | 2.7<br>1.5<br>4     | V<br>A<br>W |

| Total Power Consumption                                                          |       |         | 15                  | W           |

#### Figure 5. GPU Electrical Characteristics

| Parameter              | Specification                                                       |

|------------------------|---------------------------------------------------------------------|

| Package                | PBGA, 680 balls max at 1mm pitch, 35x35mm                           |

| Ball-Out Configuration | 5 rows of signal balls (580 balls), 10x10 central thermal GND array |

| Construction           | Encapsulated die, Chip up with bond wire substrate                  |

| Substrate              | 4-layer                                                             |

| Thermal Impedance      | θ <sub>C</sub> < 3.5 C/W                                            |

| Power Consumption      | 15W Max                                                             |

| Max Junction Temp      | 140C                                                                |

| Max Case Temp          | 88C                                                                 |

#### Figure 6. GPU Mechanical Characteristics

#### 2.4.1.1. Graphics processor

The Graphics Processor consists of the transformation and lighting engine, a pixel processing pipeline, and a rasterization unit. Included with these blocks are the memory controllers, cache controllers, and logic to connect the various computational blocks. The rasterization unit outputs a digital video signal output as a parallel bit stream clocked by the pixel clock or some multiple of the pixel clock.

Refer to the NV2A Design Specification for a detailed description of the GPU.

#### 2.4.1.2. Integrated North Bridge

The Integrated North Bridge functional block provides the system memory controller, P6 front-side bus interface, LDT bus interface, and the arbitration unit functionality. This block arbitrates between the CPU system bus and the GPU memory bus and processes the memory transactions to and from the unified memory pool. The Memory controller also bridges the CPU system bus to the PCI bus for interface to the peripheral logic and IO controllers.

The unified memory pool is implemented in 200MHz DDR SDRAM.

#### 2.4.1.3. Front Side Bus Interface

The front-side bus interface to the CPU will be a P6 bus clocked at 133MHz.

#### 2.4.1.4. LDT Bus Interface

The LDT Bus is a high-speed, low pin-count bus with dedicated upstream and downstream transfer channels. The bus is capable of combined transfers of up to 800MB/s (400MB/s up and 400MB down simultaneously).

#### 2.4.1.5. Digital Video Interface

The digital video samples will be output to the TV encoder via a 12-bit parallel digital video interface, clocked on both edges. The output format is 4:4:4 YCrCb, 4:2:2 YCrCb, or 4:4:4 YPrPb.

The GPU shall supply HSYNC and VSYNC signals to the TV encoder, but the TV encoder shall supply the pixel clock. The GPU shall output a composite sync signal used to drive the sync output of the controller ports.

#### 2.4.1.6. Clock Generator

The clock generator includes phase-locked loops for synthesizing the clock signals required for the various logical units, including the front-side bus to the CPU, the DDR memory busses, the LDT bus to the MCPX, and the GPU core clock. The high-level description of the clock generator is shown below:

Clock Input:

13.5MHz

Clock Outputs:

250/300MHz – GPU Core

200MHz – DDR, LDT

133MHz – CPU

### 2.4.2. TV Encoder

The TV Encoder takes as input digital video signals over a parallel digital interface from the GPU, and outputs analog CVBS/Y/C or Y/Pr/Pb signals. The TV Encoder section converts the analog component signals and outputs the appropriate signals to drive either a television monitor, computer monitor, or HDTV monitor, based on the settings of the configuration registers. Programming of the configuration registers is accomplished via an I<sup>2</sup>C bus connected to the core logic chip.

The TV Encoder is capable of outputting all of the modes described in the following section, which includes:

Composite and s-Video NTSC, PAL, or SECAM

Composite PAL and Component RGB (625/50) for SCART operation

Component YPrPb 480p, 720p, or 1080i HDTV

The TV Encoder supports selective application of Macrovision anti-recording signals as follows; For NTSC and PAL output modes, Macrovision 7.01 anti-recording is applied to the composite and s-Video outputs.

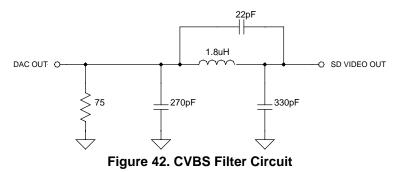

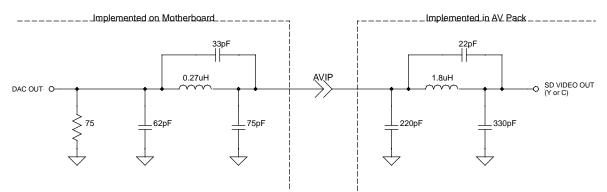

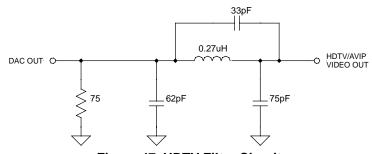

The output signals are driven on to the AVIP connector by  $75\Omega$  cable driver amplifiers. Anti-alias filtering and EMI suppression filtering is accomplished via off-chip filter networks as described in detail in the AVIP section.

The following paragraphs describe the system-level specifications for the TV Encoder. A detailed description of the TV Encoder, including electrical/mechanical characteristics and software interface are described in detail in the document entitled *Flicker-Free Video Encoder with Ultrascale Technology*.

#### 2.4.2.1. Digital Video Interface

12-bit parallel

Dual-edge clocked

1.2V signaling

$\ensuremath{\text{H/V/Field}}$  to be supplied by the GPU CRT controller logic, Pixel CLK to be generated by the TV Encoder

#### 2.4.2.2. Additional Features

Macrovision 7.0 or better for CVBS and Y/C outputs

Wide Screen Signaling

Copy Generation Management System

#### 2.4.2.3. Video Input Modes

24-bit RGB

24-bit 4:4:4 YCrCb

24-bit 4:2:2 YCrCb

HDTV 4:4:4 YPrPb (SMPTE-274M, SMPTE-296M)

#### 2.4.2.4. Video Output Modes

The television modes used by country are tabulated in Appendix C of this document. To support the countries in which Xbox is to be marketed, the TV Encoder shall support the following video output modes:

NTSC-M (CVBS + Y + C) PAL-I (CVBS + Y + C) PAL-I (CVBS + R/G/B) SECAM-L (CVBS + Y + C) HDTV (Y + Pr + Pb)

#### 2.4.2.5. Conversion Mode Matrix

The TV Encoder shall support the following combination of input and output modes:

| Fram | Frame Buffer Configuration |                       | NTSC PAL |       | HDTV |      |       |

|------|----------------------------|-----------------------|----------|-------|------|------|-------|

| Pix  | Line                       | Frame (Hz)            | NICO     | SECAM | 480p | 720p | 1080i |

| 640  |                            |                       |          |       |      |      |       |

| 704  | 480                        | 59.94 Interlaced      | •        |       |      |      |       |

| 720  |                            |                       |          |       |      |      |       |

| 640  |                            | 50.04                 |          |       |      |      |       |

| 704  | 480                        | 59.94<br>Progressive  | •        |       |      |      |       |

| 720  |                            | -3                    |          |       |      |      |       |

| 640  |                            | 50                    |          |       |      |      |       |

| 704  | 480                        | 480 50<br>Progressive |          | •     |      |      |       |

| 720  |                            |                       |          |       |      |      |       |

| 640  |                            | 50                    |          |       |      |      |       |

| 704  | 576                        | 50<br>Interlaced      |          | •     |      |      |       |

| 720  |                            |                       |          |       |      |      |       |

| 720  | 480                        | 60p                   |          |       | •    |      |       |

| 1280 | 720                        | 60p                   |          |       |      | •    |       |

| 1920 | 1080                       | 30i                   |          |       |      |      | ٠     |

Figure 7. Video Output Conversion Matrix

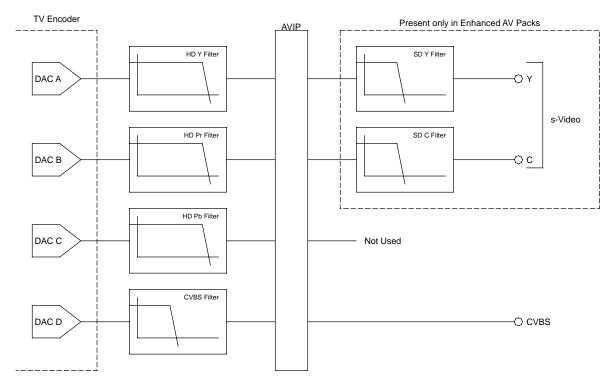

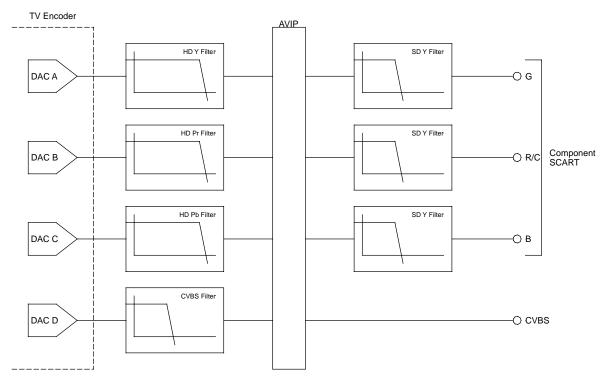

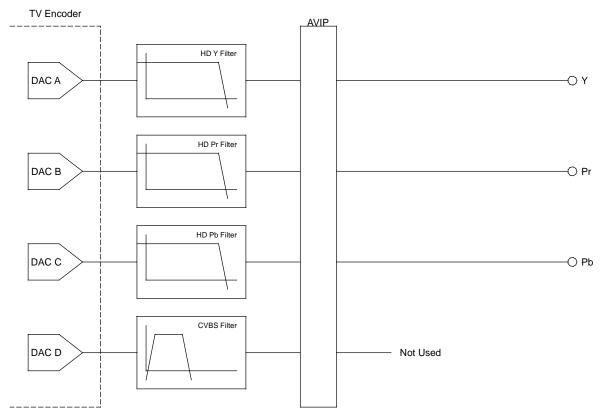

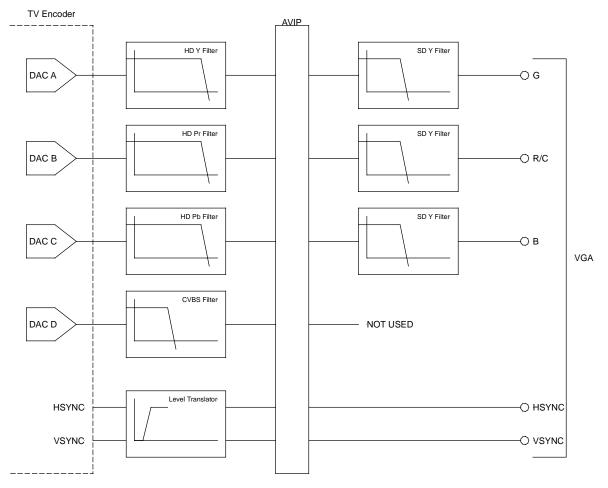

#### 2.4.2.6. Analog Video Output Multiplexing

The TV Encoder provides four video DAC outputs. To support all the composite, s-Video, and component modes, the four outputs must be multiplexed. The DAC multiplex table is shown below:

| DAC Output | SDTV Mode | SCART Mode | HDTV Mode |

|------------|-----------|------------|-----------|

| DACA       | Y         | G          | Y         |

| DACB       | С         | R          | Pr        |

| DACC       | Not Used  | В          | Pb        |

| DACD       | CVBS      | CVBS       | Not Used  |

#### Figure 8. DAC Output Allocations

Each TV Encoder DAC output is capable of driving a single  $75\Omega$  terminated load. Passive filtering is required to minimize EMI and spectral aliases arising from the digital to analog conversion. The filter arrangements and characteristics are described in the AVIP section.

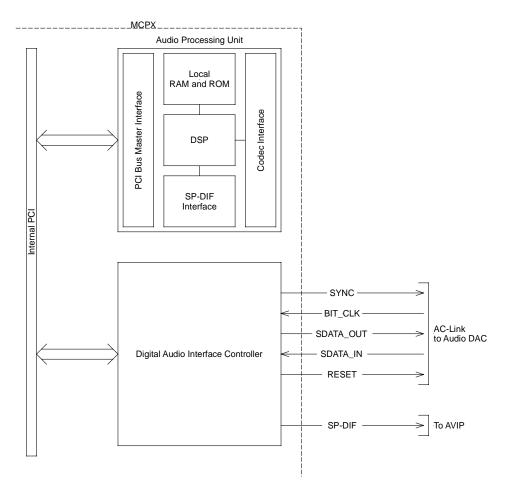

# 2.5. Audio Subsystem

The audio subsystem consists of an Audio Processor Unit (APU) and a digital audio interface controller. The APU and digital audio interface controller are integrated into the system core logic chip MCPX.

Figure 9. Audio Subsystem Block Diagram

The capabilities of the audio subsystem include:

Advanced Audio Processor – Synthesis, effects, and mixing operations are performed by a dedicated APU.

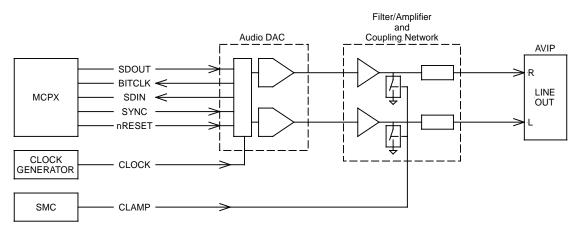

**AC-Link Out** – The audio subsystem shall output two-channel AC-Link audio to the audio DAC. The performance and characteristics of the DAC are described in the AVIP section...

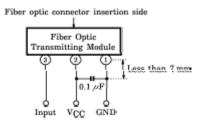

**Electrical SP-DIF Output** – The audio subsystem shall provide electrical SP-DIF output for interface to an external optical SP-DIF driver. The optical SP-DIF transmitter shall be implemented as part of an AV expansion pack as described in the accessories section of this document. The SP-DIF interface may be used for stereo or AC-3 encoded 5.1 channel modes.

The detailed specification of the individual subsystem components is contained in the following sections.

### 2.5.1. Audio Processing Unit

The Audio Processing Unit is integrated into the core logic chip (MCPX). The APU consists of a fixed-function DSP and two programmable DSP's. The DSP's can access audio streams in system memory, have local code and data memory, and output the processed streams back to system memory for output via the AC-Link and SP-DIF interfaces.

Input Formats 1-18 Samples per block 8, 16, and 32-bit containers DX8 Capabilities Sub-Mix Bins 2<sup>nd</sup> Pass Processing <u>2D Wave</u> Direct Sound, WAVE Per-Voice Filtering Output Formats 1, 2, 4, 6 Samples per block 16 or 32-bit containers

3D Support HRTF with Cross Talk I3DL2 Reverb Occlusion and Obstruction Near Field Affects Real-Time AC-3 Encode <u>Voice Support</u> 256 Total Hardware Voices 64 3D voices with cross over 32 DX8 sub-mix voices with hardware submixing160 2D/WT voices, all DLS2 capable 20 effects and input voices

#### Performance

DLS1/2 Support

**DLS** Filtering

Two envelope engines w/LFO

Pan, Pitch, Vibrato, Tremolo

Reverb and Chorus send

133MHz Clock frequency Fixed-function 24-bit DSP @ 2000MIPs Programmable-function 24-bit DSP @ 500MIPs for effects processing Programmable-function 24-bit DSP @ 500MIPs for real-time AC-3 Encode +85dB with 16bps inputs 24-bit sample processing paths 32-bit mixing

#### Figure 10. APU Feature Summary

### 2.5.2. Digital Audio Interface Controller

The Digital Audio Interface Controller provides the DMA engine and interface for outputting the processed audio streams to the audio outputs. The audio subsystem provides digital audio in two formats: SP-DIF and AC-Link.

The AC-Link interface is compliant with revision 2.1 of the AC-Link interface specification. The AC-Link digital audio stream is converted to an analog signal by an audio DAC. The DAC, post filtering, and audio performance characteristics are described in detail in the AVIP section.

The AC-Link drives an AC-97 audio codec that provides analog line-level audio outputs to the AVIP. The details of the digital to analog converter and related signal conditioning circuits are discussed in detail in the AVIP section.

The audio subsystem outputs a logic-level (3.3V) SP-DIF signal that is presented to the AV Interface connector. Conditioning of this signal for electrical or optical transmission via coax or optical fiber is accomplished in the AV-Pack.

The analog and digital output streams may be separate, so it is possible to output unencoded stereo via the analog interface while simultaneously outputting AC-3 encoded multi-channel audio via the SP-DIF.

Software Note:

Due to incompatibilities between pre-AC-3 digital amplifiers and current digital amplifiers, this output must be configurable such that AC-3 output can be blocked. If AC-3 encoded audio is input to a pre-AC-3 digital amplifier, the amplifier erroneously interprets the AC-3 encoding as PCM audio samples, and the result is high-level noise being fed to the speakers. There is a possibility of damage associated with this scenario, so the default configuration should be to force all digital output to be PCM.

An alternative implementation is to default the SP-DIF output to disabled, then force the user to select one mode or the other. This would reduce the chance that a user with an AC-3 compatible system would miss out by not enabling the AC-3 output mode.

# 2.6. Core Logic (MCPX)

The Core Logic, or Media/Communications Processor (MCPX) contains all of the core logic functions, including the audio processor and interface controller, hard disk and DVD drive interfaces, USB controllers, and system support functions. The MCPX connects to the GPU via an LDT bus that provides 800MB/s transfer rate. The individual logic blocks integrated into the MCPX core logic chip are described in the following sections.

| Parameter                                                                      | Min  | Typical | Max                | Unit        |

|--------------------------------------------------------------------------------|------|---------|--------------------|-------------|

| Core and LDT Power Supply<br>V1P5<br>I <sub>V1P5</sub><br>Power Consumption    | 1.45 | 1.5     | 1.65<br>TBD<br>TBD | V<br>A<br>W |

| LVTTL Interface Power Supply<br>V3P3<br>I <sub>V3P3</sub><br>Power Consumption | 3.0  | 3.3     | 3.6<br>TBD<br>TBD  | V<br>A<br>W |

| RTC Battery Power Supply<br>V <sub>BAT</sub><br>I <sub>BAT</sub>               | 0.9  | 1.5     | 1.5<br>4           | V<br>μA     |

| Total Power Consumption                                                        |      |         | 2                  | W           |

| Case Temperature (T <sub>CASE</sub> )                                          | 0    |         | 88                 | С           |

#### Figure 11. MCPX Electrical Characteristics

| Parameter              | Specification                                      |

|------------------------|----------------------------------------------------|

| Package                | PBGA, 340 balls max at 1mm pitch, 23x23mm          |

| Ball-Out Configuration | 5 rows with 6x6 core array of power/gnd            |

| Construction           | Encapsulated die, Chip up with bond wire substrate |

| Substrate              | TBD                                                |

| Thermal Impedance      | TBD                                                |

| Power Dissipation      | 2W Max                                             |

| Max Case Temp          | 88C                                                |

#### Figure 12. MCPX Mechanical Characteristics

The following sections describe the functionality of the core logic functions. Refer to the nVidia MCPX Data Sheet for a detailed description.

## 2.6.1. Audio Processor and Digital Audio Interface

These logic blocks are described in the Audio Subsystem description.

### 2.6.2. ATA Interface

The MCPX implements a single ATA-100 port with scatter-gather mastering. The master supports the following transfer modes:

PIO Mode 0, 1, 2, 3, and 4

DMA Mode 0, 1, and 2

UDMA-33, 66, and 100

The Xbox motherboard and cable assemblies will be designed only for ATA-33 operation, using the DMA-33 transfer mode.

## 2.6.3. USB Host Controller

The MCPX implements a USB host controller compatible with the Open Host Controller Interface (OHCI) 1.0a implementing the Universal Serial Bus protocol, version 1.1. The host controller is mapped to the four game controller ports.

The USB differential transceivers are implemented directly on the core logic IC. Power management and overcurrent protection is provided by external power management IC's. The host controller monitors the overcurrent flags from the power management circuit. The port power enable signals are controlled on each port individually by GPIO pins.

The MCPX actually implements two USB host controllers. The second host controller is unused in the production version of the Xbox, but is mapped to a fifth port on development units to provide debug information.

This port may be eliminated entirely in a future version of the MCPX chip, so it should never be utilized by an Xbox application.

# 2.6.4. Ethernet MAC

The Ethernet MAC features dual-speed CSMA/CD for 10 and 100 Mb/s operation as defined in IEEE 802.3u. The MAC includes a Media Independent Interface (MII) to an external PHY.

The features of the MAC include:

Provides transmit FIFO to provide frame buffering for increased system latency, automatic retransmission with no FIFO reload, automatic transmit padding, and FCS generation

Provides receive FIFO to provide frame buffering for increased system latency, automatic flushing of collision fragments, automatic receive pad stripping, and a variety of address match options

Supports Unicast, Multicast, and Broadcast addressing

Supports filtering for at least 16 multicast addresses

Offers two-part deferral algorithm

Recognizes late collision

Provides internal and external loop-back

The MII Interface Features:

Compliant with IEEE 802.3u (MII/RMII)

Supports half- and full-duplex operation

Controls and receives status from external PHY through the MII management interface

Supports auto-negotiation through the external PHY

Supports automatically polling the status of external PHY status including Link Status, Autonegotiation ability, Half and Full Duplex ability.

## 2.6.5. General Purpose IO Pins

The MCPX Implements 9 General Purpose IO Pins. The GPIO pins provide software control of functions by the CPU. The GPIO pins have the following general DC characteristics. Refer to the MCPX data sheet for detailed information.

| Parameter                                                                                                               | Min  | Typical | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------|---------|-----|------|

| Output Voltage Characteristics<br>V <sub>OL</sub> @ I <sub>OUT</sub> = 4mA<br>V <sub>OH</sub> @ I <sub>OUT</sub> = -1mA | 3.0  |         | 0.3 | V    |

| Input Voltage Characteristics<br>V <sub>IL</sub><br>V <sub>IH</sub>                                                     | 0.8  |         | 2.0 | V    |

| Input Voltage Range                                                                                                     | -0.5 |         | 5.5 | V    |

Figure 13. GPIO DC Electrical Characteristics

The GPIO pins are mapped as tabulated below:

| GPIO | Signal Name | Direction | Comment                                                                                                                                                                               |

|------|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | FWENB       | OUT       | This pin is reserved to allow for in-system re-programming<br>of the Flash-ROM in development systems only. This pin<br>shall not be terminated in the retail version of the product. |

| 1    | VBUSENB1    | OUT       |                                                                                                                                                                                       |

| 2    | VBUSENB2    | OUT       | These pins provide per-port control of the VBUS power                                                                                                                                 |

| 3    | VBUSENB3    | OUT       | enable for each of the five controller/expansion ports.                                                                                                                               |

| 4    | VBUSENB4    | OUT       |                                                                                                                                                                                       |

| 5    | VBUSENB5    | OUT       | This pin provides port control of the VBUS power for the fifth port. This port is only installed on development units.                                                                |

| 6    |             |           |                                                                                                                                                                                       |

| 7    |             |           |                                                                                                                                                                                       |

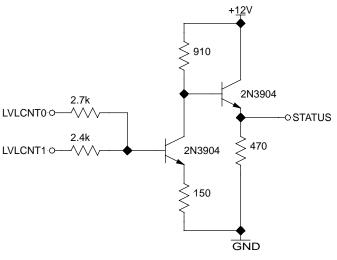

| 8    | LVLCNT0     | OUT       | These pins provide control of the SCART STATUS output                                                                                                                                 |

| 9    | LVLCNT1     | OUT       | of the AVIP port.                                                                                                                                                                     |

#### Figure 14. GPIO Pin Usage

### 2.6.6. Internal Boot ROM

The MCPX includes a 512-byte ROM mapped to the reset vector of the CPU address space. This ROM overlaps the top 512 addresses of the external ROM.

## 2.6.7. External ROM Interface

The MCPX shall support addressing of up to 16MB of external Flash ROM, EEPROM, or masked ROM. The interface is implemented as a simplified X-Bus interface, with only memory read/write capability and no interrupt or DMA support.

The bus consists of the following pins:

ADDRESS[23..0] – 24 Address lines are supplied by MCPX, 21 address lines are connected on board to address up to 2M addresses.

DATA[7..0] – 8 Data lines for reading and writing data from and to the bus.

CS - A single chip select to qualify access cycles

MEMR - A memory Read qualifier signal

MEMW – A memory Write qualifier signal

Note:

Although the MCPX External ROM Interface can address up to 16MB of ROM, the motherboard design only wires 21 address bits to the ROM component. This allows up to 2MB of ROM to be installed on the motherboard, and since the upper address lines do not affect the chip select qualification, the external 2MB ROM will be aliased 8 times in the 16MB address space.

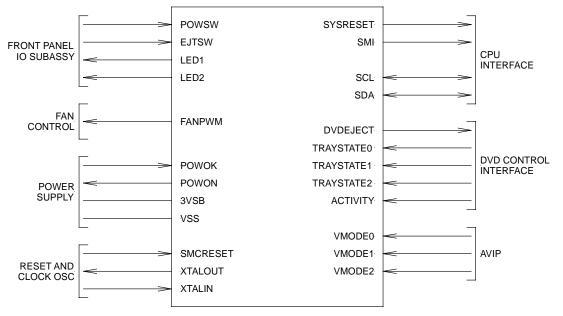

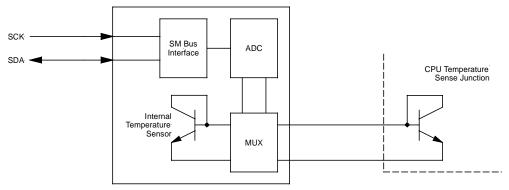

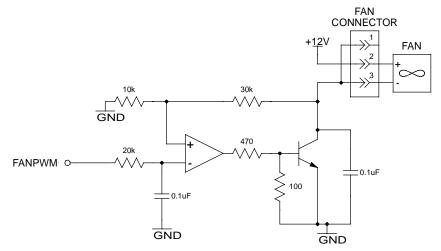

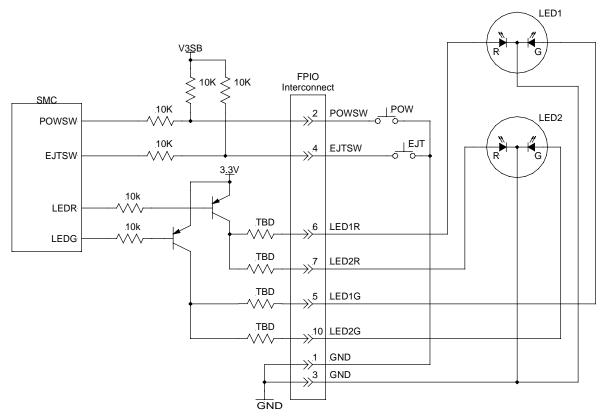

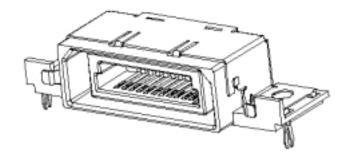

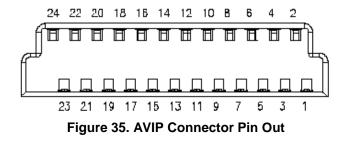

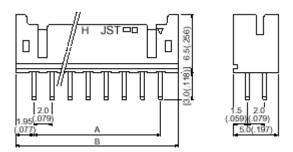

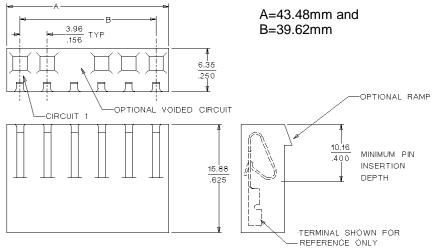

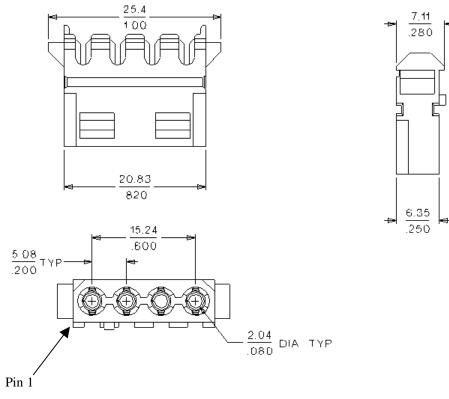

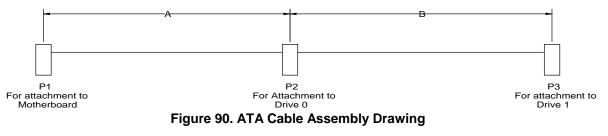

The External ROM may alternatively be interfaced to the MCPX via the LPC interface. See the note in the following section describing how to enable this interface.